初识 TileLang

文章目录

今天在看 vLLM SHenzhen Meetup 视频直播的时候,看到北大吴童对 TileLang 的分享,感觉很有意思,就去了解了一下。

一个好的学习方法,是带着问题去学习。刚听到 TileLang 的时候,我有这么几个问题:

今天在看 vLLM SHenzhen Meetup 视频直播的时候,看到北大吴童对 TileLang 的分享,感觉很有意思,就去了解了一下。

一个好的学习方法,是带着问题去学习。刚听到 TileLang 的时候,我有这么几个问题:

- 什么是 TileLang?

- 为什么需要 TileLang? 说是做 AI 算子的,算子不是硬件实现的吗?

什么是 TileLang?

TileLang 在 Github 上面的介绍是:

Domain-specific language designed to streamline the development of high-performance GPU/CPU/Accelerators kernels.

简单来说,它是简化高性能GPU/CPU内核的开发的领域编程语言。主持人串场的时候,又是说算子又是说内核(kernel),让我有点晕,后来才知道,算子是内核的抽象,内核是算子的具体实现。网络查找的资料如下:

在深度学习和神经网络中,算子和Kernel是两个密切相关但有本质区别的概念,它们分别承担不同的角色。

算子是指一种运算逻辑的抽象表示,用于描述数学运算或操作。例如,加法、卷积、池化等都可以看作是算子。算子定义了输入、输出以及计算逻辑,是深度学习模型的基本组成单元,用于构建神经网络的各个层和组件。

Kernel则是算子的具体实现,负责在硬件上执行算子的运算逻辑。Kernel直接与底层硬件交互,执行诸如矩阵乘法、卷积等高效的数学运算。不同的硬件平台(如CPU、GPU、TPU)可能需要不同的Kernel实现,以充分利用硬件的计算能力。

主要区别

抽象层次:算子是逻辑层面的抽象,描述了运算的功能;Kernel是物理层面的实现,负责具体的计算。

硬件依赖性:算子与硬件无关,而Kernel通常是硬件特定的,针对不同硬件平台进行优化。

实现方式:算子可以通过框架(如TensorFlow、PyTorch)定义,而Kernel需要用底层语言(如C++、CUDA)实现,并进行优化。

优化目标:算子关注模型的功能和结构,Kernel则关注计算效率和硬件性能。

实际应用

在深度学习框架中,算子和Kernel的协作是模型高效运行的关键。例如,卷积算子定义了卷积操作的逻辑,而Kernel则通过优化算法(如Winograd、FFT)和硬件特性(如SIMD、Tensor Cores)来加速卷积运算。

通过这种分工,开发者可以专注于算子的设计,而框架则负责为不同硬件生成高效的Kernel实现,从而提升模型的性能和适应性。

为什么需要 TileLang?

对于这个问题,我在看了 Gemini 的解答,对为什么需要 TileLang 的理解是:

- 简单来说,硬件提供的是通用内力,也有些厂商,会对某些特定的算子提供专用电路去优化实现。

- 不是所有的算子都有加速电路的,而且一些新设计的算子,还是需要通过程序,编排通用的设备计算单元来实现。

- 而且,有些算子的优化,是需要在硬件层面,通过编排,来实现的,比如,矩阵乘法,需要通过编排,来实现矩阵乘法的加速。

- 还有一点就是,算子是一种逻辑抽象,需要编写 kernal 来实现,不同的设备平台,需要不同的 kernal 来实现,跨平台实现非常麻烦,tilelang 能够简化这个过程。

原始答复如下:

简单来说,硬件提供了“能力”,而 TileLang 这样的工具是用来“指挥”硬件以最高效的方式发挥这种能力的“说明书”或“编排语言”。

我们来分解一下这个问题:

1. 硬件层面:GPU 能做什么?

- 矩阵乘法单元(Tensor Cores): 是的,像 NVIDIA GPU 里的 Tensor Cores 或 Google 的TPU,它们是专门为执行大规模矩阵乘法(MatMul)和累加操作而设计的硬件电路。它们极其快速,是 AI 计算的核心。

- 通用计算核心(CUDA Cores): 除了专用单元,GPU 还有成千上万个通用的并行计算核心。

- 内存层次结构: GPU 有不同速度的内存,比如超高速但容量很小的共享内存/缓存(Shared Memory/Cache)和速度较慢但容量巨大的全局内存(Global Memory)。

关键点: 硬件本身只提供这些基础的计算和存储能力。它就像一个拥有成千上万名小计算员的办公室,每个计算员算得飞快,但你必须给他们下达极其精确、协调一致的指令,他们才能高效地完成一个复杂的任务。

2. 软件层面:如何指挥硬件?

一个 AI 算子(Operator, Op),比如卷积(Convolution)或者一个复杂的激活函数,并不仅仅是一个单一的矩阵乘法。它通常是一系列操作的组合:

- 从全局内存中读取数据。

- 可能需要对数据进行重排或变形。

- 执行核心的数学计算(可能是矩阵乘法,也可能是加法、指数等)。

- 将计算结果写回全局内存。

这就是矛盾所在:

- 性能瓶颈: 访问全局内存非常慢(相比于计算速度)。如果数据流没有被精心设计,GPU 就会把大量时间浪费在等待数据上,而不是在计算,这就是所谓的“内存墙”问题。

- 算子多样性: AI 领域在飞速发展,每天都可能诞生新的、奇特的算子(比如新的注意力机制、新的归一化方法)。这些新算子并没有现成的、由硬件厂商(如 NVIDIA)手写的优化库(如cuDNN)。

3. TileLang 的作用:高效的“指挥官”

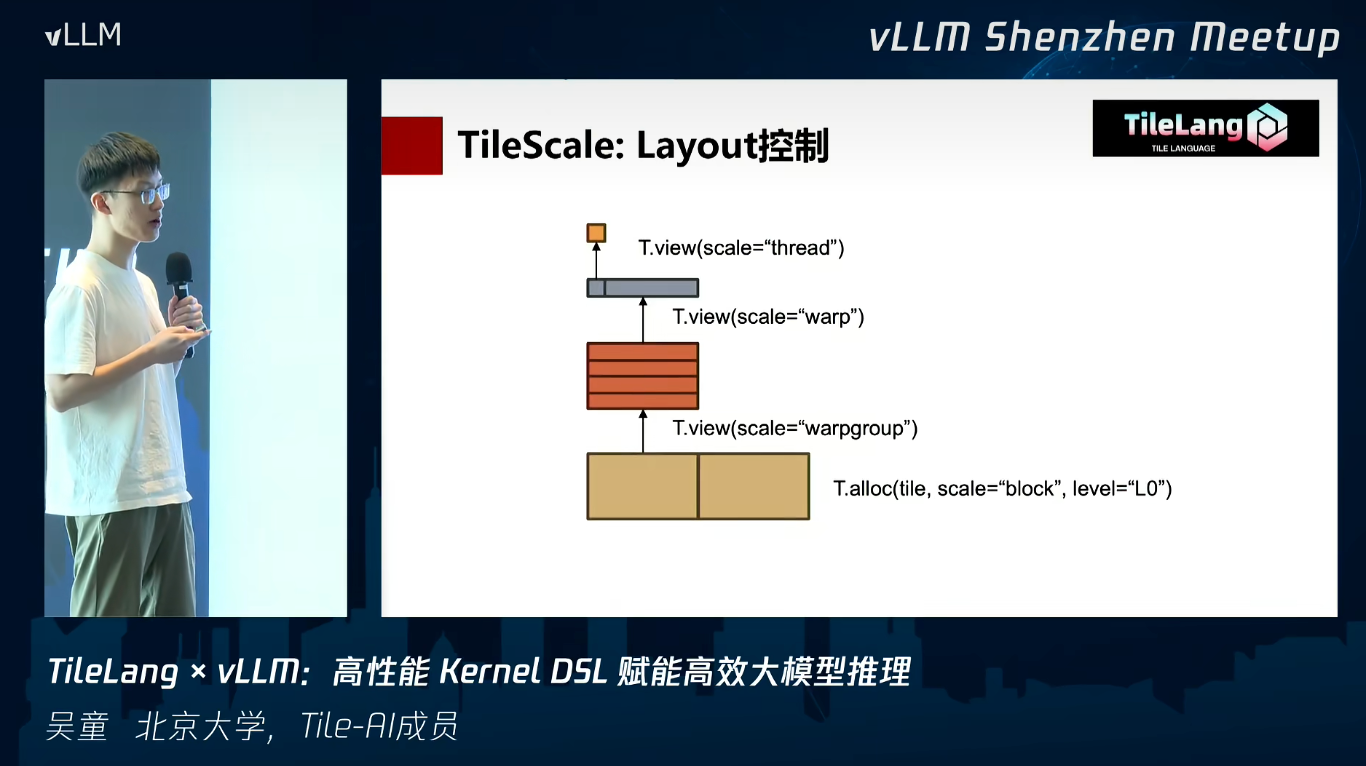

TileLang 就是为了解决上述矛盾而生的。它是一种领域特定语言(DSL, Domain-Specific Language),专门用来编写 AI 计算内核(Kernel)——也就是在 GPU 上运行的具体指令集。

它的核心思想是 Tiling(分块):

将一个大的计算任务(比如一个巨大的矩阵乘法)分解成许多小的“瓦片(Tile)”。每个小“瓦片”的数据可以被加载到 GPU 核心旁边的高速共享内存中。GPU 核心们在这个小瓦片上完成计算,然后再去处理下一个瓦片。通过这种方式,可以最大化地利用高速缓存,最大限度地减少对慢速全局内存的访问,从而实现极致的性能。

所以,TileLang 解决了什么问题?

- 性能优化: 它让开发者能用一种相对高级的语言,精细地控制数据如何在 GPU 的不同内存层级之间移动和计算,编写出性能媲美甚至超越硬件厂商手写库的算子代码。对于矩阵乘法这种“标准”算子,它可以榨干硬件的最后一滴性能。

- 算子创新和灵活性: 当研究人员提出一个新算子时,他们不再需要等待 NVIDIA 更新 cuDNN 库。他们可以使用 TileLang 或类似的工具(如 OpenAI Triton)快速地为这个新算子编写一个高性能的 GPU Kernel,从而可以快速地在 PyTorch 或 TensorFlow 这样的框架中进行实验和部署。

- 跨平台/硬件可移植性: TileLang 的目标之一是实现“一次编写,到处运行”。你用 TileLang 写的算子逻辑,理论上可以被编译到不同的后端硬件上(NVIDIA GPU, AMD GPU, 甚至其他 AI 芯片),而不需要为每种硬件重写底层的 CUDA 或 ROCm 代码。

文章作者 疯魔慕薇

上次更新 2025-08-30